cache_arm_x86

ARM架构

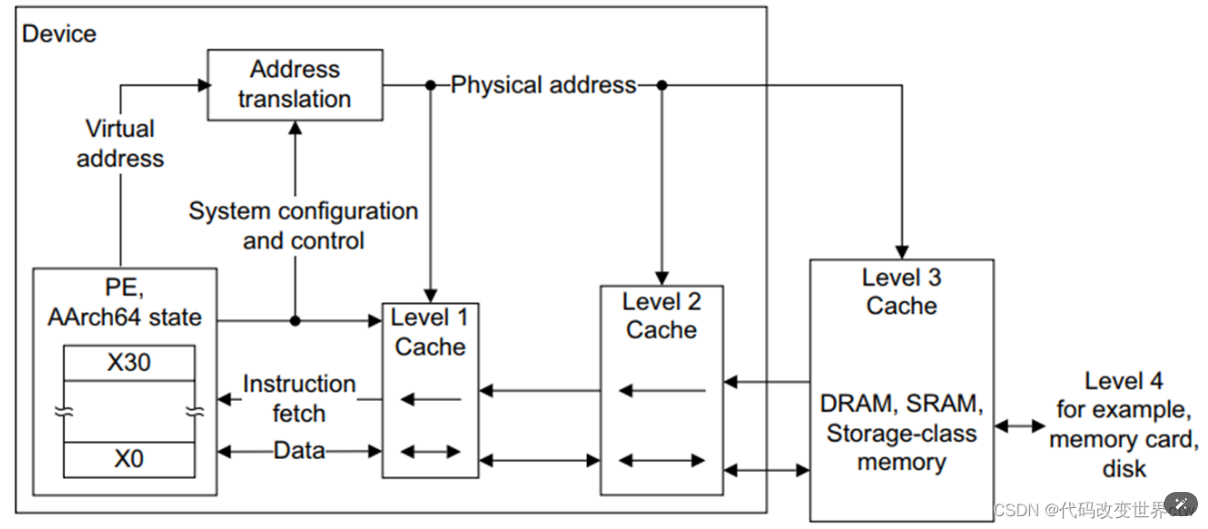

cache多级相连

cache是多级的,在一个系统中会有多级cache。

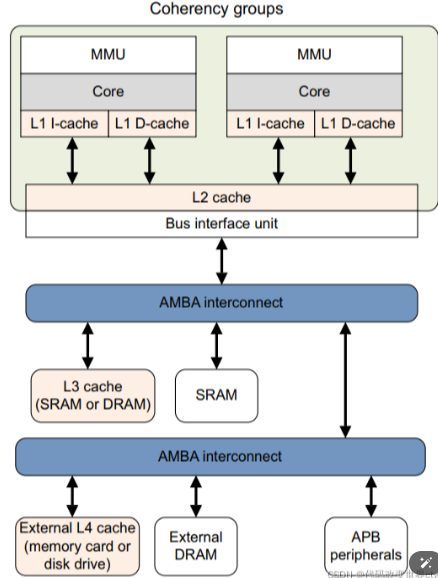

一般来说,在bit-little中,L1在core中,且L1缓存又分为 I-cache指令环境和 D-cache数据缓存。L2 cache在cluster中,L3则在BUS总线上。

当CPU计算时,首先去L1去寻找需要的数据,如果没有则去L2寻找,接着从L3中寻找,如果都没有,则从内存中读取数据。所以,如果某些数据需要经常被访问,那么这些数据存放在L1中的效率会最高。

计算机缓存行cache line

高速缓存其实就是一组称之为缓存行cache line的固定大小数据块。其大小是以突发写或者突发读的周期大小为基础的。

即使处理器只存取一个字节的存储器,高速缓存控制器也启动整个存取器访问周期并请求整个数据块。缓存行第一个字节的地址总是突发周期尺寸的倍数。缓存行的起始位置总是与突发周期的开头保持一致。

当从内存中取单元到cache中时,会一次取一个cacheline大小的内存区域到cache中,然后存进相应的cacheline中。

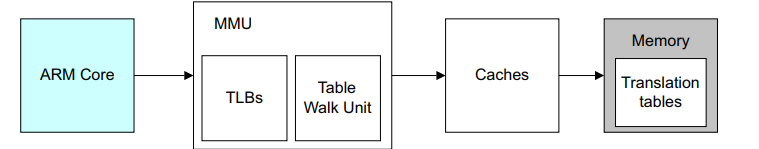

cache一般和MMU结合使用

很多时候cache都是和MMU一起使用的(即同时开启或关闭)。因为MMU的页表entry属性中控制着内存权限和cache缓存策略等等。

在ARM架构中,L1 cache都是VIPT(virtual index physical tag 虚拟地址做索引,物理地址做tag)的,也就是当有一个虚拟地址送进来,MMU在开始进行地址翻译的时候,Virtual Index就可以去L1 cache中查询了,MMU查询和L1 cache的index查询是同时进行的。如果L1 Miss了,则再去查询L2,L2还找不到则再去查询L3。 注意在arm架构中,仅仅L1是VIPT,L2和L3都是PIPT。