pll

PLL原理

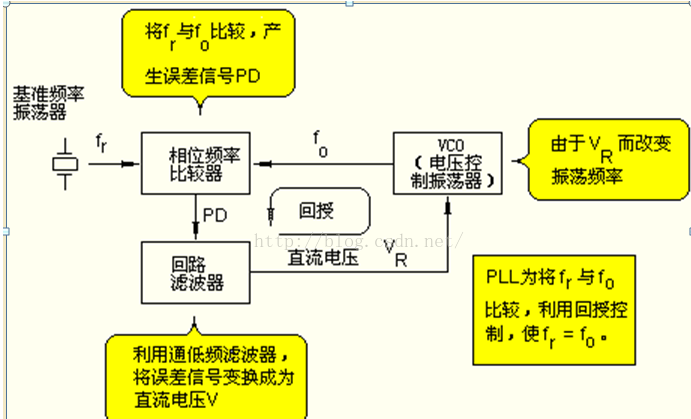

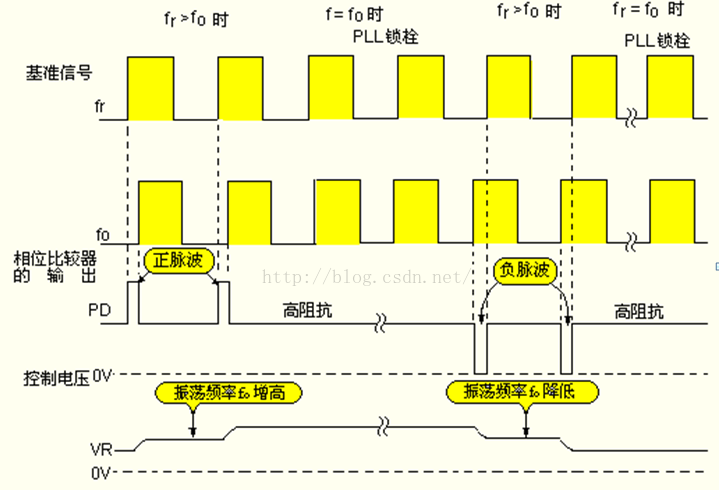

由一个基准频率振荡器(晶体振荡器),相位频率比较器,VCO(电压控制振荡器),回路滤波器组成。晶振产生频率为fr的时钟,与VCO产生的fo的时钟同时传入相位频率比较器中进行比较,产生比较结果以脉冲波的形式传入回路滤波器,回路滤波器通过低频将脉冲波转变为直流低压VR,传入VCO对fo进行控制,形成反馈控制电路。

当fr>fo时产生PD为正脉冲,VR变大,当fr<fo时,PD产生负脉冲波,VR减小,形成对fo的闭环控制,最终目的,是fo==fr。

倍频器

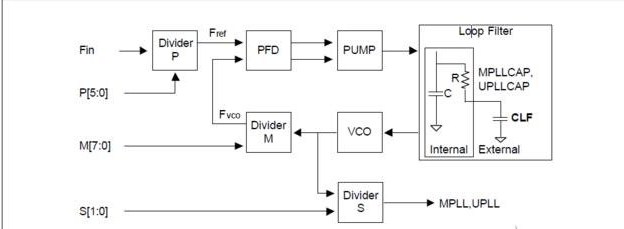

PLL的主要功能还是倍频。倍频的实现其实很简单,只要在VCO的后面加一个分频器,时参与比较的Fvco=(1/n)fo,fo’是VCO产生的。这样就实现了Fvco=n*fr。

分频器原理

分频器原理就是之前上的简单的数电知识,在这就一块说了。

主要就说一个偶数分频。

偶数分频器的实现简单,用计数器在上升沿或者下降沿计数,当计数器的值等于分频系数的一半或等于分频系数时,信号翻转。

电路原理是用一个上升沿计数的计数器,每次计数到2时输出信号clkout翻转一次,每次计数到4时clkout再翻转一次,一直周期重复下去。其他的偶数分频器原理也是一样。